1. DDR4 Memory Overview

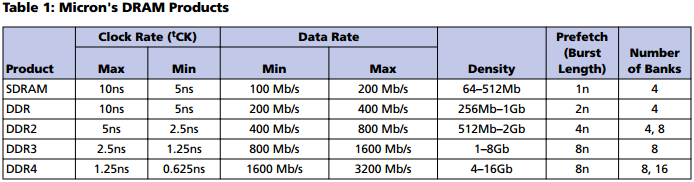

DDR4 是2014年9月推出的当今主流的内存标准,DDR5 预计将于2020年发布,因此在未来的2-3年内,DDR4还是硬件设计中的生力军。首先,从Micron SDRAM的产品线直观感受下不同代际 SDRAM 特性的对比。

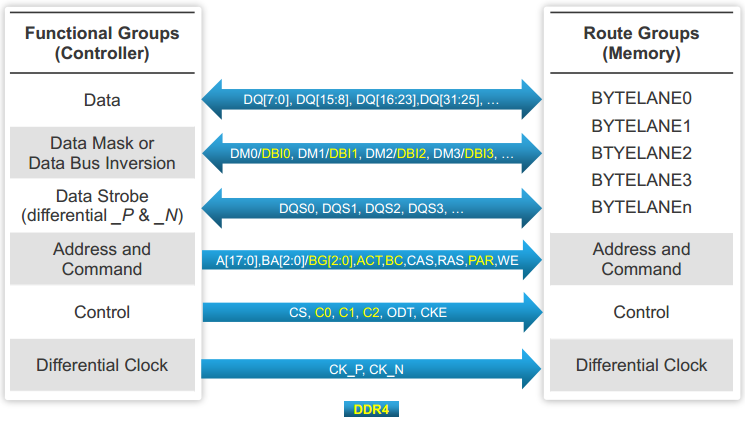

DDR4信号分组情况如下,黄色标识信号为DDR4相比DDR3新增的信号。

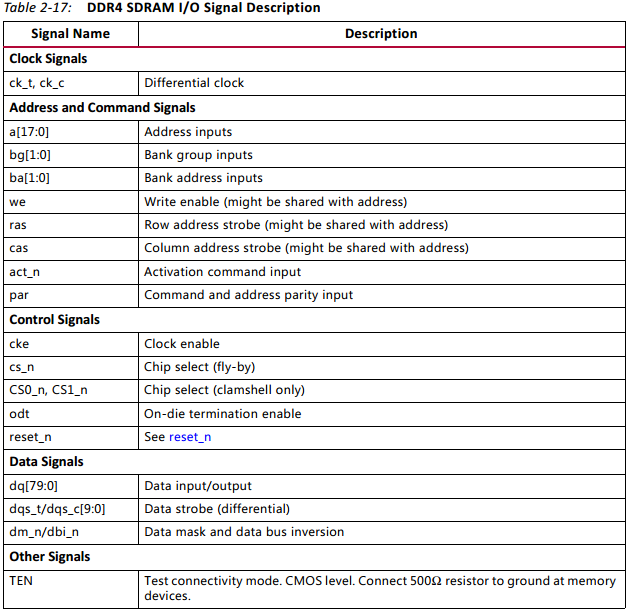

信号定义如下表示:

2. DDR4 Bus Topologies

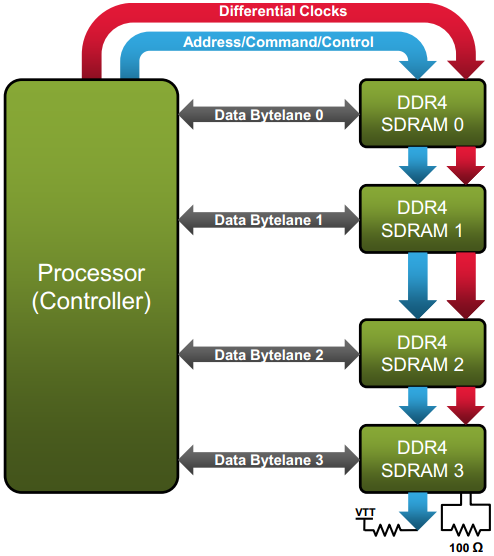

- On-board SDRAM

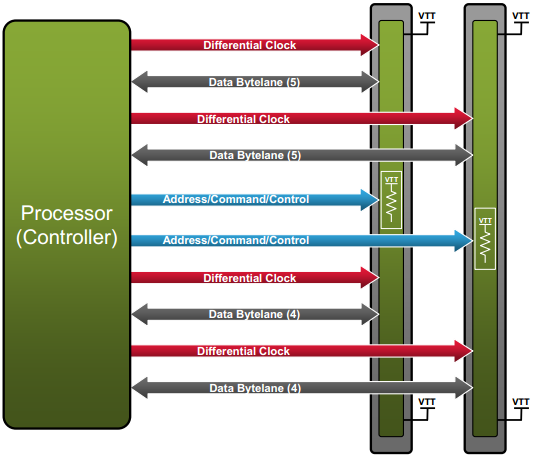

- On-board two-UDIMM

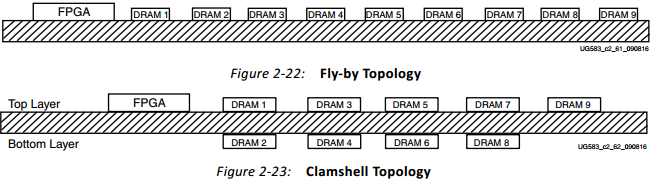

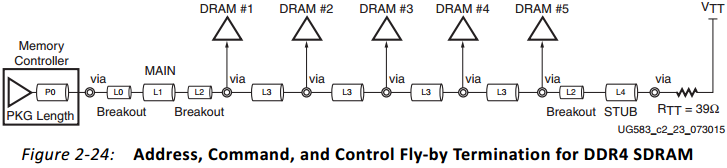

在PCB上,DDR4 Layout分为所有内存颗粒在单面的 Fly-By 拓扑和双面的 Clamshell 拓扑。Fly-By 拓扑更易于信号走线,信号完整性更好,但占用单板空间较大;Clamshell 拓扑更节约空间,但对走线要求更高,适用于对空间要求严格的应用场合。

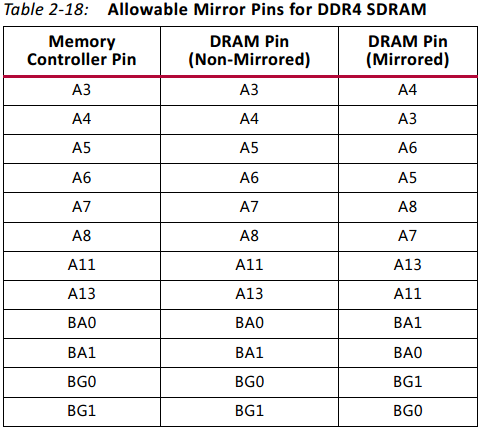

对于 Clamshell 拓扑的走线,由于内存颗粒PIN分布对称的特性,地址线在换层时造成地孔不足、桩线过长等信号完整性问题,为此 JEDEC 规范定义 Address Mirroring 功能,允许调换DRAM特定地址管脚的功能。下表列出的是DDR4 SDRAM中可以调换的地址引脚。

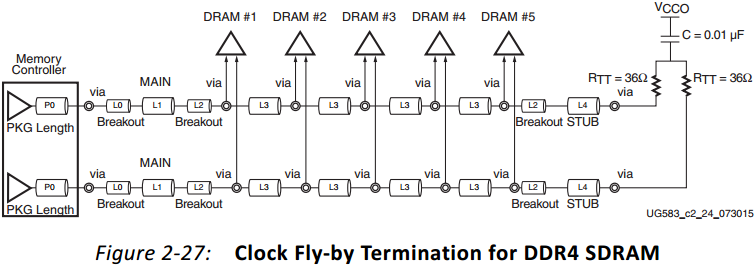

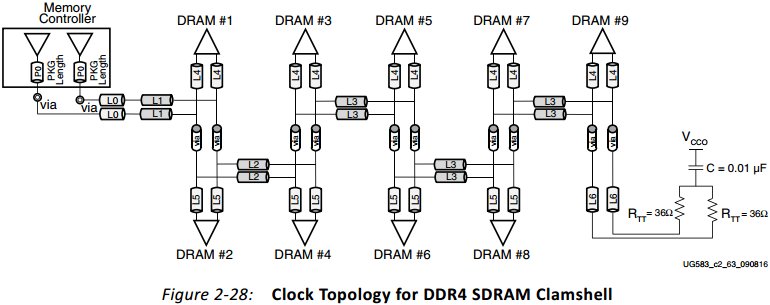

下面两张图分别为时钟信号(CK_T/CK_C)在 Fly-By 和 Clamshell 两种拓扑结构下走线及端接的示意图。

3. Routing Constraints/Trace Matching

DDR4在单板上的走线约束分两类:

- Total length/delay constraints -总的走线长度的约束

- Skew constraints -偏差约束,即信号组内或组间的等长约束

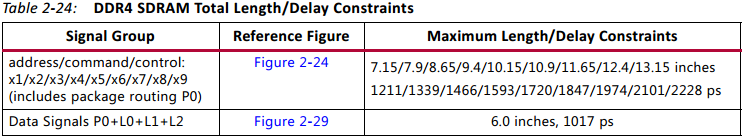

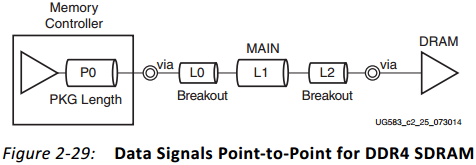

在 UG583 文档中,XILINX 说明其对于 Total length 的要求如下,分别针对地址/控制信号和数据信号。

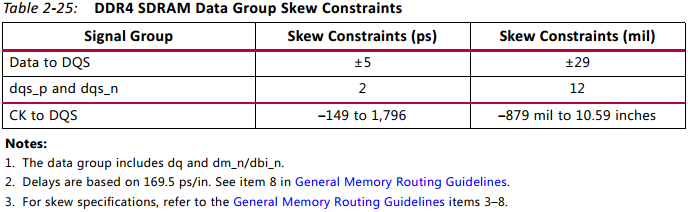

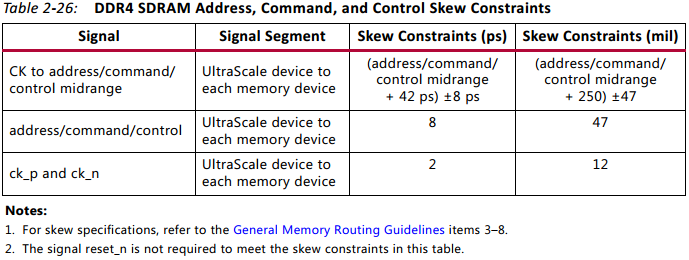

对于 Skew constraints ,即数据信号和地址/控制信号的等长约束如下:

参考资料

- Routing DDR4 Interfaces Quickly and Efficiently -Cadence

-

UG583: UltraScale Architecture PCB Design User Guide -Xilinx