用Cadence OrCAD Capture绘制原理图的第一步是建立器件的Symbol,对于管脚数目少的器件,可以通过常规的方法建立Symbol(右键New Part)。然而,对于CPU、FPGA这些动辄上千Pin的器件,如果使用常规方法,不但浪费时间,而且正确性也难以保证。有些半导体公司提供的设计资料包括Symbol,但也有的公司只提供器件封装的TXT文件,这时候在用OrCAD绘制原理图之前,就必须先创建器件的Symbol。下面以XILINX FPGA为例,简要说明如何快速地创建器件的Symbol。

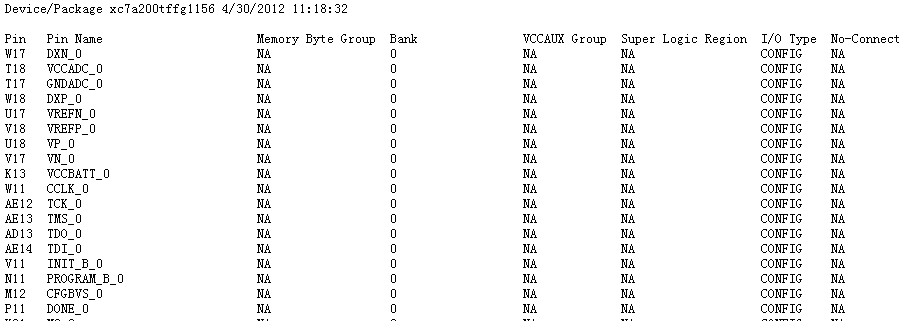

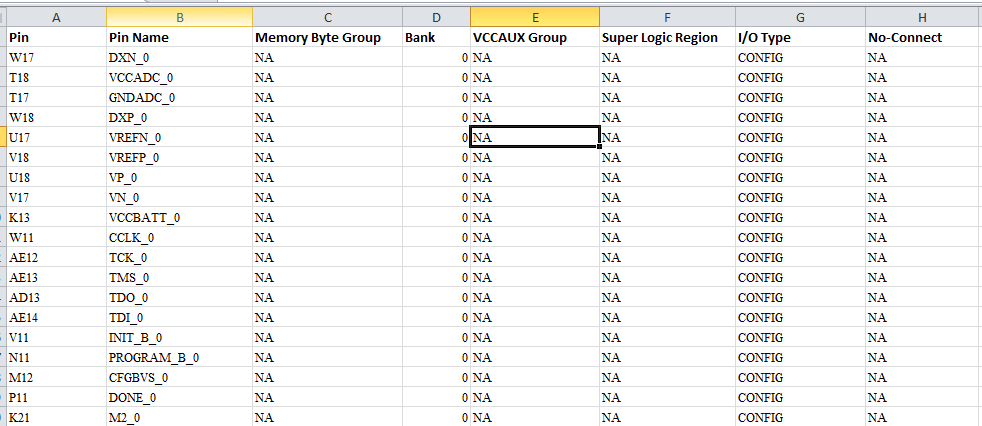

在Xilinx网站下载的封装源文件:xc7a200tffg1156pkg.txt,如表1:

表1. 封装源文件

创建流程如下:

Step 1:编辑封装源文件

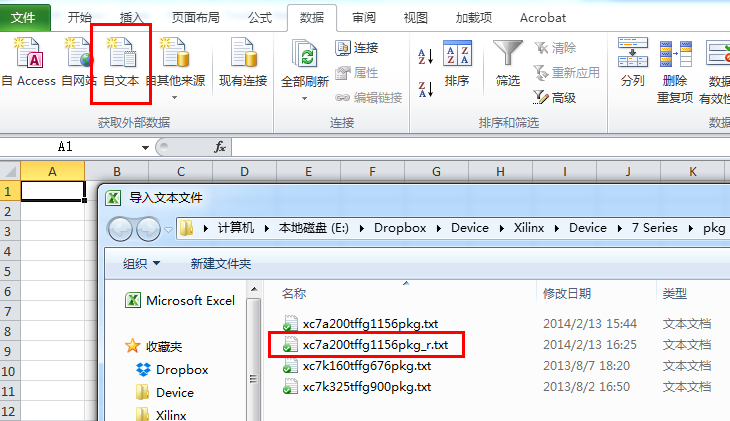

1. 将文本文档导入到EXCEL打开,图1;

图1. 将文本文档导入到EXCEL打开

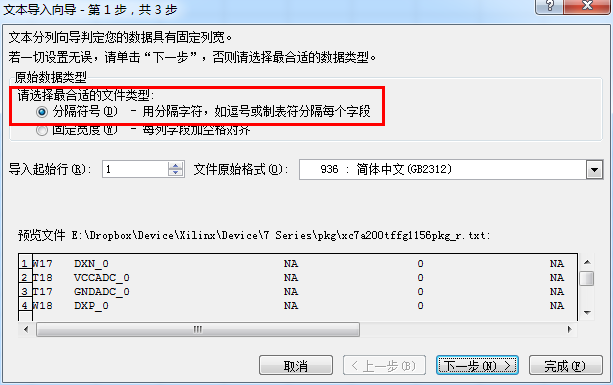

2. 导入设置,图2;

图2. 导入EXCEL设置

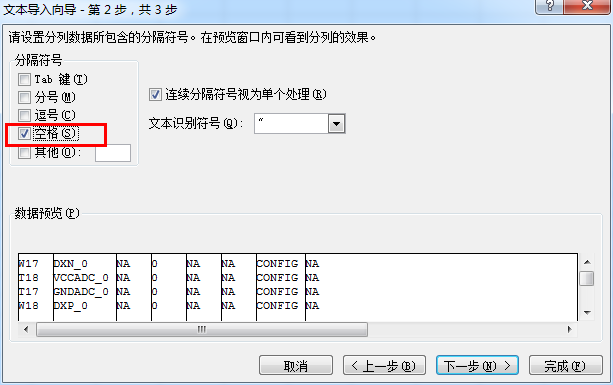

3. 分隔符号选择。根据实际下载的封装文件情况选择分隔符号。图3;

图3. 选择分隔符号

4. EXCEL打开的封装源文件,图4;

图4. EXCEL打开的封装源文件

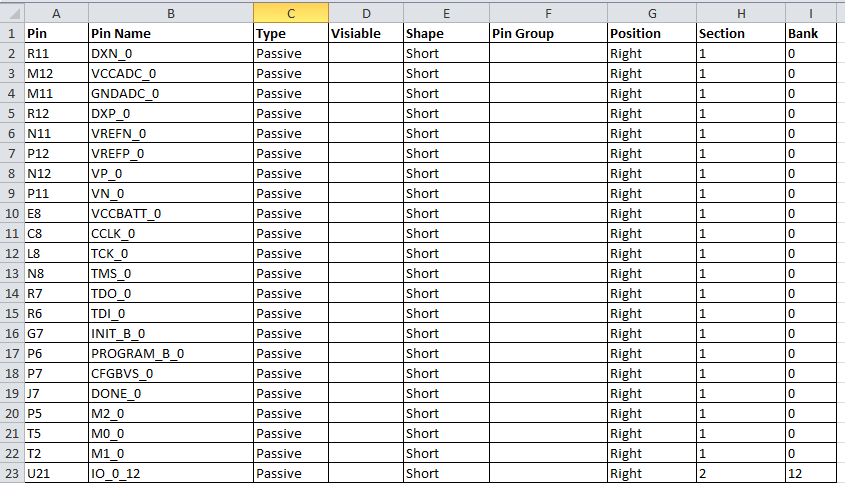

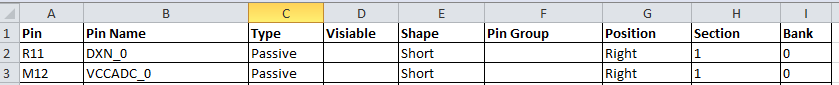

5. 以上1-4步骤无外乎是将TXT格式的器件封装源文件,用EXCEL打开,以便删减部分行/列信息,做成OrCAD Capture自动生成Symbol需要的格式。关于格式说明(列定义),参考本文表格说明部分。最终EXCEL文件格式如图5(注:粘贴板复制到Capture时候不需要最后一列Bank,这是Xilinx器件的Bank,检查Symbol时参考使用):

图5. OrCAD建立封装的文件格式

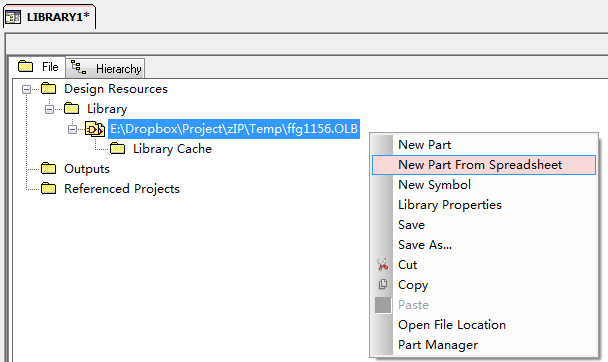

Step 2:导入封装库信息到OrCAD Library

6. OrCAD Capture生成Library界面如图6,因为我们最终要做的是把EXCEL内容粘贴到这张Spreadsheet,选择New Part From Spreadsheet:

图6. OrCAD Capture生成Symbol界面

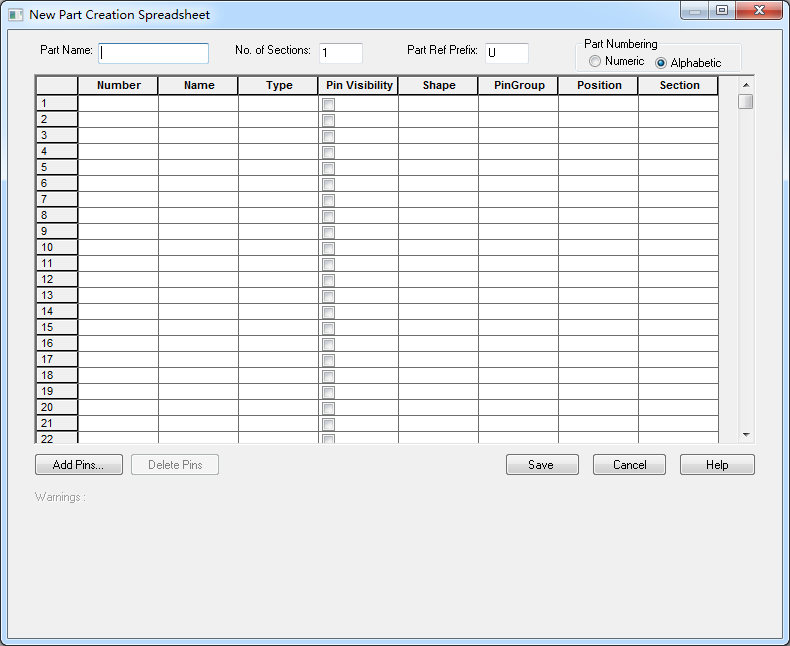

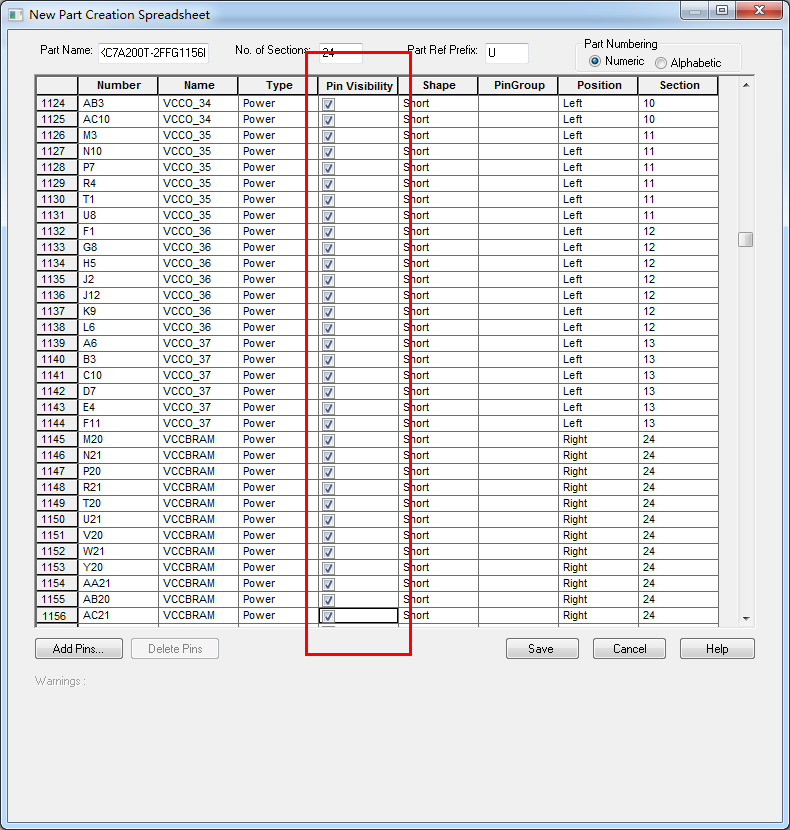

7. 将图5内容粘贴到Spreadsheet内,点Save即可完成封装的生成,图7;

图7. 将编辑好的EXCEL内容粘贴到Spreadsheet

表格说明

器件封装EXCEL文件各列的含义及填写说明,图8:

1. Type:

信号 - Passive 电源和地 - Power

区别在于:Type为Power的管脚,信号名可以重复。一般情况下,所有管脚都填Passive对线路图和Layout没有影响;

2. Visiable:不填;

3. Shape:Symbol脚的尺寸,填Short;

4. Pin Group:不填;

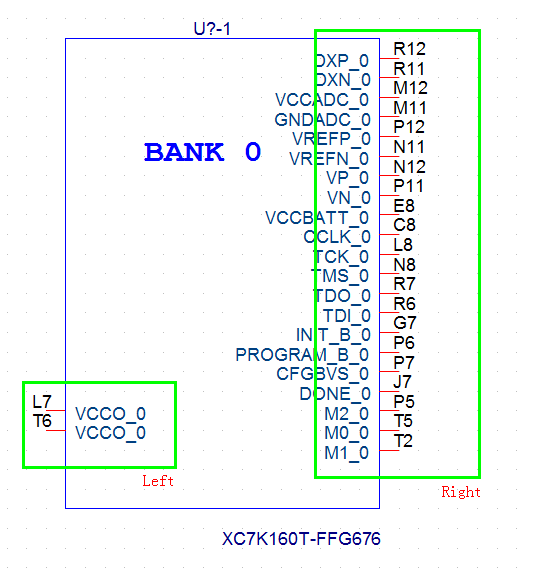

5. Position:管脚在Symbol图所处的位置,可选Bottom/Left/Right/Top,电源Pin一般放左边(一般所有GND/NC都放在一个Section,那么记得在这个Section里选一半的脚放在Right,一半的脚放在Left,这样生成的Symbol管脚是对称的),如图9示;

图9. Symbol Position属性示意

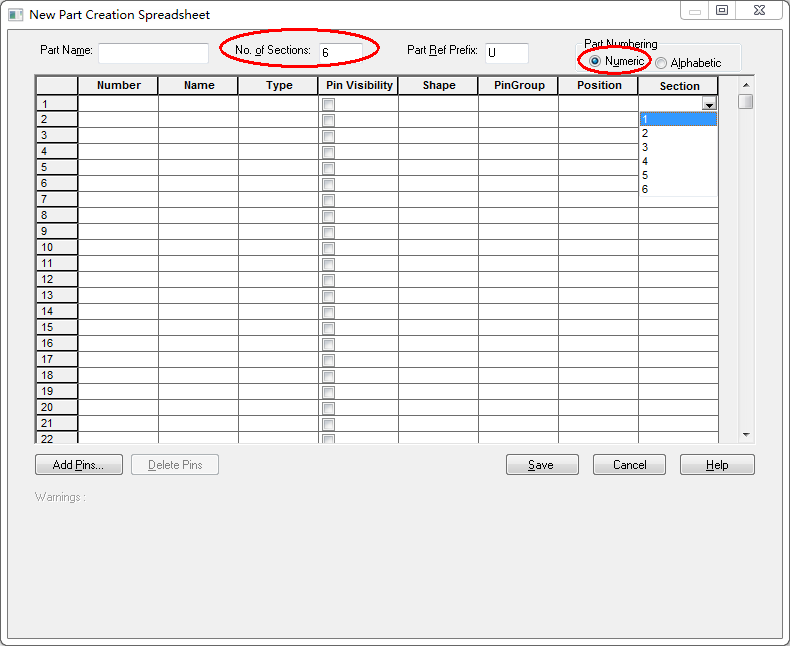

6. Section:整个Symbol分多少部分,一般按不同的功能划分,比如Power/GND/PCI/SERDES等等。从1开始算起,比如示例图5的Symbol的Bank 0被标记Section为1。注意,在OrCAD Spreadsheet设置Section的数目填写应和EXCEL中Section数目一致,如图10示;

图10. Symbol Section属性示意

注意

1. 关于 OrCAD的Pin Type:

The default pin Shape (Line) and Type (Passive) are OK for most pin types. For clocks and active low signals you may want to use some of the other shapes. You will also want to use the type Power for power pins. When you do this, make sure that the Pin Visible check box is checked. Also, I usually like to place my power pins near the top of the part and ground pins near the bottom. As a last touch, double-click the text that reads <value> and change it to read XC9536-PLCC44. When you are all done, your part should look something like the following symbol.

2. Pin Visibility可以 Ctrl + C 然后 Ctrl + V ,先点很长一列√,然后复制即可!

图11. Pin Visibility属性

3. XILINX FPGA补充:

- XILINX有的BANK的PIN顺序很乱(BANK 0和GT BANK),需要在Symbol中手动把顺序改过来便于绘制原理图;

- XILINX FPGA不同型号芯片有许多Footprint兼容的,找资料的时候选择其中管脚最多的,按照它做,其它低等级器件这些位置NO Connect即可