PCI Express(PCIe)是PCI-SIG协会定义的点对点串行通信协议,当前在桌面、服务器、嵌入系统以及网络通信领域已得到广泛应用。PCIe的一大优势是其可扩展带宽和灵活的时钟结构。本文将介绍PCIe不同的时钟分配方案以及各自优势。

PCIe链路

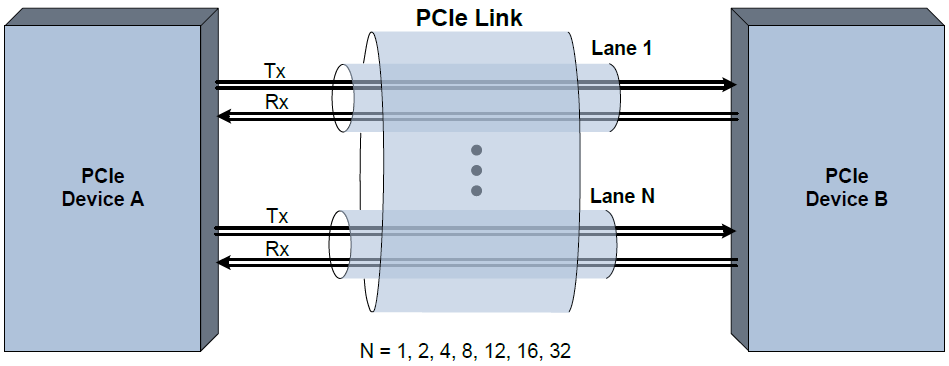

在讨论PCIe时钟分配前,先简要介绍PCIe链路(Link)。PCIe链路包括一个或多个通道(Lane),每个通道又包括发送(Tx)和接收(Rx)两个方向的差分信号对。图1表示最简单PCIe链路的组成。PCIe很大的优点是链路宽度(通道数)的可扩展性,每个链路最大可扩展到32个通道。

图1. PCI Express链路

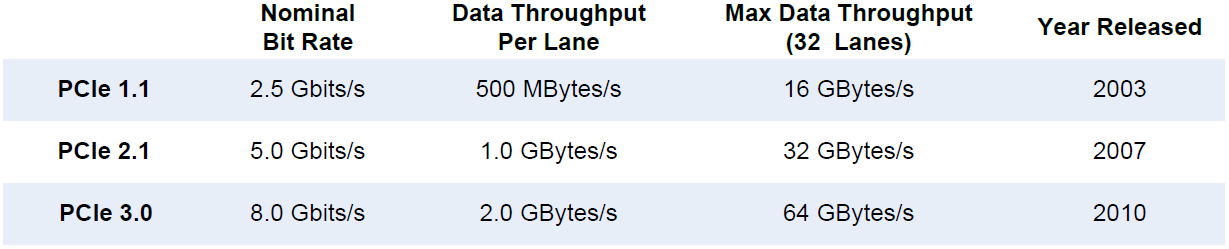

PCIe 3.0支持单通道单向数据传输速率达8Gbits/s,最高数据吞吐量64GByte/s(32 Lane+双向)。低带宽需求的应用可以用较少的通道达到设计需求。PCIe 1.1和2.1单通道单向数据速率分别为2.5Gbps和5.0Gbps。选择高版本PCIe意味着在同等数据传输速率下,设备之间可以用更少的通道,但高版本的PCIe对时钟有更高的要求。下文将探讨这些需求的不同。表1列出不同版本PCIe的特点。

表1. PCIe各版本对比

注:

- Nominal Bit Rate,单向数据传输速率,也可表示为GT/s,即Gigabit Transfers/S,表示数据传输过程中每秒Level Transitions(0-1, 1-0)的次数;

- Data Throughput Per Lane,表示单通道双向数据的吞吐量。在Nominal Bit Rate计算的基础上,考虑到双向,需要乘以2倍;

- PCIe 1.1和PCIe 2.0采用8b/10b编码,PCIe 3.0采用128b/130b编码,不同的编码方式数据传输的效率不同,前者8/10=80%,后者128/130=98.5%;

- 计算示例(PCIe 2.1):Data Throughput Per Lane = 5 Gbits/s(Bit Rate) * 2(Bidirectional) * 0.8 (8b/10b Efficiency) / 8(Bit to Byte) = 1.0 GBytes/s;

- PCIe采用8b/10b或128b/130b编码方式,从数据中恢复时钟,PCIe 1.1/PCIe 2.1/PCIe 3.0时钟频率分别1.25/2.5/4.0GHz(每个时钟周期有0-1和1-0两次Level Transition)

PCIe应用

未完成

原文链接

http://www.silabs.com/Support%20Documents/TechnicalDocs/PCIe-Clock-Source-Selection.pdf