概述

Load Switch,即负载开关,是指可以用来开启和关闭系统电源的电子电路(Electronic Relay),它既可以由分立元器件搭建,也可能是集成式的负载开关芯片。在电路系统中,使用负载开关可以实现更有效的电源管理,包括时序控制和节能等目的。与此同时,负载开关还可能包括诸如降低待机模式的漏电流、抑制上电浪涌、防止电源反向和控制下电时快速放电等特性。因此,负载开关得以广泛应用于消费、车载等电子设备。

本文主要介绍负载开关的基本原理、应用和技术参数,并比较分立式电路方案和集成式负载开关芯片的区别。

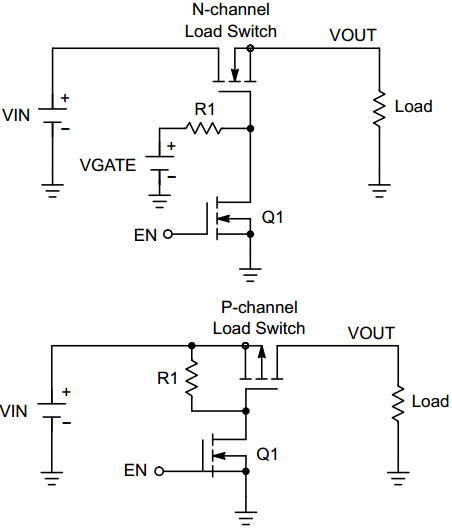

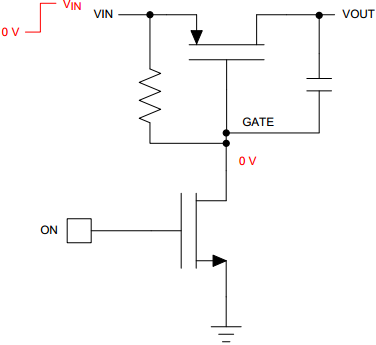

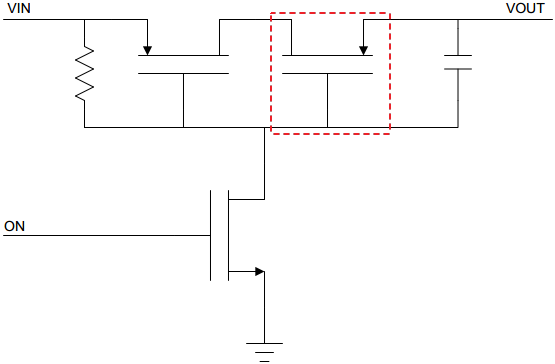

负载开关的构成主要包括两部分:开关晶体管和开关控制电路。其中,开关晶体管通常为 MOSFET,它既可以是 PMOS,也可能为 NMOS;开关控制电路因开关晶体管导通条件不同,也可能存在差异,以匹配不同控制信号的特点(高或低有效,电平),这块也叫 Level Shift 电路,将在下文详述。图1表示负载开关的基本电路图。由于负载开关在上电后即开始工作,因此要求它的漏电流必须小,同时要求其导通电阻尽可能小,以减小工作时的热耗散。

图1. 负载开关の基本电路

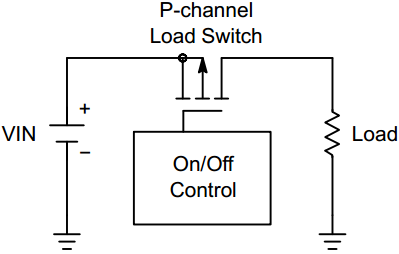

负载开关芯片,即实现负载开关功能的芯片方案。相比于由分立电路搭建的负载开关,负载开关芯片集成度更高,既可以简化电路设计、减小元器件占用 PCB 面积,而且还可能实现部分由分立电路比较难实现功能。

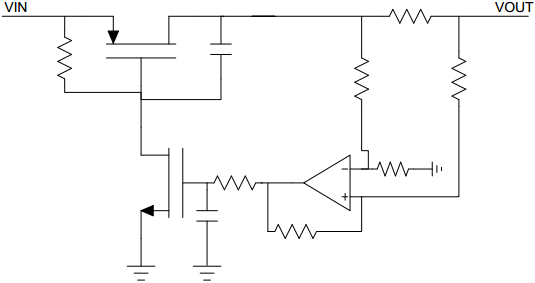

如图2所示负载开关芯片的内部框图,它可能包括以下几个部分:

- 开关晶体管,它决定负载开关可能接受的最高输入电压和最大续流能力,MOSFET 的 Rds(on) 直接决定负载开关的电源热耗散。另外,MOSFET为 P 型或 N 型将决定负载开关内部控制电路的结构;

- 门极驱动电路,通过控制 MOSFET 的门极的充放电,实现控制负载端电源上电时间的目的;

- 控制逻辑电路,由负载开关芯片外部的信号驱动,以控制负载开关芯片的开启或关闭,以及其它如快速放电、Charge Pump 和保护电路模块等;

- Charge Pump,仅出现于由 N 型 MOSFET 构成的负载开关内,因为N型MOSFET开启时要求 Vgs 为正电压,即门极电压>源极电压(VOUT);

- 快速放电电路,在负载开关断开电源与负载时开启,通过将输出端由片内电阻接地,迅速放电,达到保护负载端电路的目的;

- 其它特性,如电源反向保护,热保护,限流保护等

应用

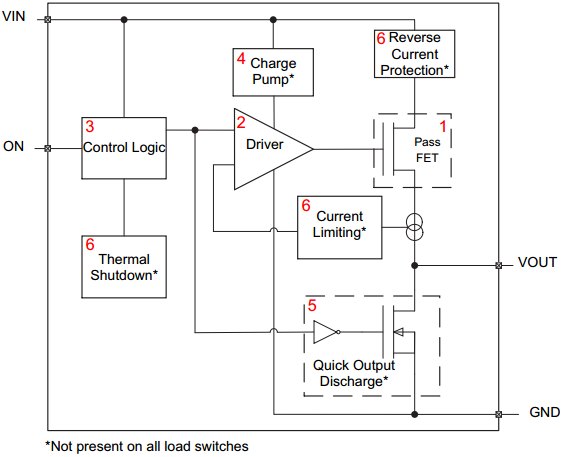

在负载开关的应用中,根据负载开关相对于电源和负载的位置,大致可分为图3表示的五种类型。说明如下:

- 低边开关(Low Side Switch),指位于负载与地之间的负载开关。低边开关从负载吸收电流;

- 高边开关(High Side Switch),指位于电源(VBAT)与负载之间的负载开关。高边开关为负载提供驱动电流;

- 推挽半桥开关(Push Pull Half Bridge),包括一个高边开关和一个放电路径开关,主要应用于要求快速停用(Quick deactivation)的场合,例如刮水器;

- H桥式开关(H Bridge),包括两个高边和两个低边开关,主要应用于正反向驱动负载的场合,例如双向马达。如图4所示的 H 桥式开关电路,打开 Q2 和 Q3 时,在马达上施加的是正向电压,而打开 Q1 和 Q4 时,则为反向电压,马达反向旋转;

- 串行开关(Serial),包括一个高边和一个低边开关,针对应用在安全要求高的场合,例如气囊爆管和临界阀,任何异常状态(如短路到地)都可能引起严重的后果。

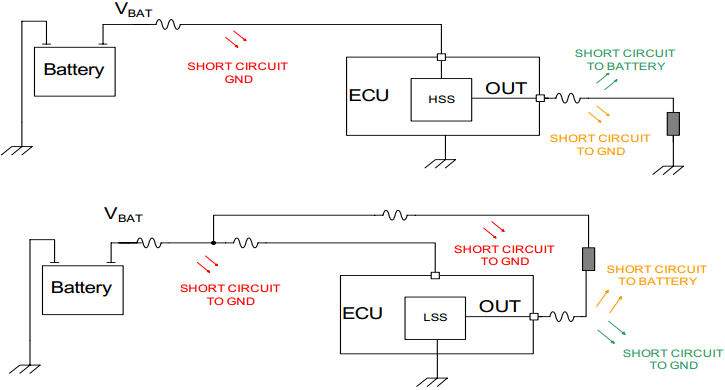

在车载领域,高边开关相比于低边开关有着更广泛应用,原因有两方面:短路保护和系统成本。

在汽车,电路短路(Short Circuit, SC)到地的可能性要高于短路到电源,因此应用高边开关相比于低边开关有更高概率应对短路问题。如图5列出汽车电子系统可能的短路场景,绿色标记的短路会导致负载一直处于 ON 状态,橘黄色标记的短路会对负载开关施加压力,而红色标记的短路会对整个电路系统造成危害。

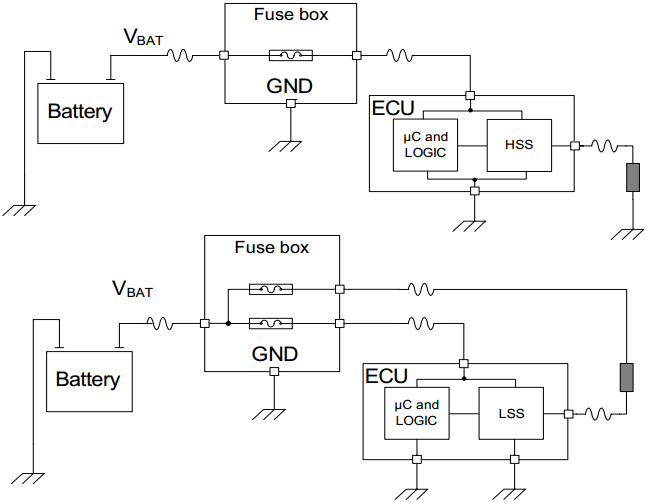

虽然对于同等的封装和 Rds(ON),低边开关的成本比高边开关更低,但是从系统级考虑,高边开关却更加经济。如图6示意高边低边开关方案的架构的对比,在低边开关的方案中需要额外的线缆和保险丝。

另外,在对电镀腐蚀(Galvanic Corrosion)敏感场合,由于在 OFF 状态下,高边开关直接切断电源与负载的联系,不存在电镀腐蚀;而应用低边开关的负载,无论在 ON/OFF 状态,它都是连接到电源上,经年累月受潮湿等环境影响,更易产生电镀腐蚀。

图6. 高边开关和低边开关系统级成本的对比

关于高边和低边开关的选择,不可一概而论,要视应用具体情况定,链接有详细解说,待研究。

技术参数

晶体管类型

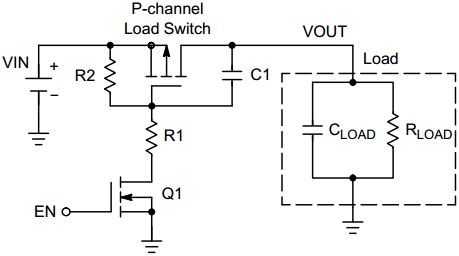

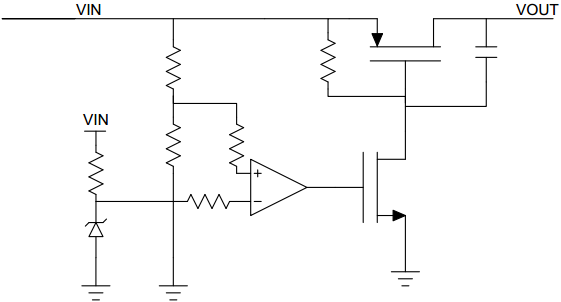

负载开关选择N型或P型晶体管由应用的特点决定。NMOS 的载流子为电子(electrons),相比于 PMOS 的空穴(holes)的移动性更佳。在相同结面积下,N型晶体管的 Rds(ON) 和栅极电容更小。因此,在大电流的场合更常见使用 N 型晶体管。如下图7所示 N 型和 P 型负载开关的控制电路。

- 对于 N 型晶体管开关,其漏极(Drain)接电源,源极(Source)接负载,负载开关的输出电压即:Vs = Vout。N型晶体管开关要求 Vgs 大于晶体管的开启门限电压 Vth ,也就是 Vg > Vout + Vth 时,才能打开晶体管。也就是说,对于N型晶体管开关需要另外一路高于输入电压的电源,以控制开关的闭合和断开。N型负载通常应用于低压输入,或者更高电压的场合——只要保证Vgs大于晶体管开关门限电压;

- 对于 P 型晶体管开关,其源极接电源,漏极接负载。晶体管开启时要求 Vsg 大于晶体管的门限电压 Vth,即 Vin > Vg + Vth 。这里近似将晶体管导通时的门极电压 Vg = 0V 。相比于N型晶体管,P型晶体管开关的应用有个显而易见的好处,只要保证 Vin > Vth 即可满足晶体管导通,而不必像N型开关需要额外的电压来实现开关控制。

图7中的限流电阻 R1 典型值 1~10K,以控制 Q1 导通时电源(Vgate or Vin)对地电流在毫安级以内。

图7. N-Channel 和 P-Channel Load Switch 电路图

图7. N-Channel 和 P-Channel Load Switch 电路图

效率

在负载开关中,电源耗散主要源于开关晶体管的导通阻抗 Rds(on),MOSFET的导通阻抗通常在几十毫欧以内。导通阻抗越低,电源耗散越低,电压输入到输出的压降越低。电源耗散和输出压降的计算公式如下:

![]()

![]() 如前文述,在同等结面积条件下,N 型晶体管比 P 型晶体管的 Rds(on) 要小一半左右。对于大电流应用,这点区别相当重要,但对于低电流应用,考虑到控制电路更加简单,P型晶体管的Rds(on)偏高的劣势可以忽略不计。简单举例,30mΩ 的 N 型晶体管和 50mΩ 的 P 型晶体管的外形尺寸相当,以下分别计算在高电流和低电流应用中它们效率的对比。

如前文述,在同等结面积条件下,N 型晶体管比 P 型晶体管的 Rds(on) 要小一半左右。对于大电流应用,这点区别相当重要,但对于低电流应用,考虑到控制电路更加简单,P型晶体管的Rds(on)偏高的劣势可以忽略不计。简单举例,30mΩ 的 N 型晶体管和 50mΩ 的 P 型晶体管的外形尺寸相当,以下分别计算在高电流和低电流应用中它们效率的对比。

- 负载电流 10A。对于 N 型晶体管,其电源耗散为3W,压降 300mV;对于 P 型晶体管,其电源耗散为 5W,压降 500mV

- 负载电流 2A。对于 N 型晶体管,其电源耗散为 120mW,压降 60mV;对于 P 型晶体管,其电源耗散为 200mW,压降 100mV

- 负载电流 850mA。对于 N 型晶体管,其电源耗散为 21.7mW,压降 25.5mV;对于 P 型晶体管,其电源耗散为 36.1mW,压降 42.5mV

由此可见,在低电流应用场合,N 型晶体管 Rds(on) 偏低的优势并不明显。在具体应用中,要考虑到实际电路的情况综合考虑。目前 P 型晶体管的 Rds(on) 工艺可低至 8mΩ,可极大提高负载开关的效率,并降低输出电压的压降。

浪涌电流

浪涌电流(Inrush Current)是指包括容性负载的负载开关,在开关导通瞬间,由于容性负载充电而产生的冲击电流,容性负载例如蓄电池或 DC/DC 电路。图8表示包括容性负载的负载开关的电路图。如果浪涌电流过大,超出负载设备的承受能力,则可能引起设备损坏。浪涌电流会造成输入电压突降,进而也可能影响整个电路系统的稳定。浪涌电流的大小直接受通流晶体管开关速度的影响,计算公式如下:

其中,C 是负载电容值,dV 是输出电压,dt 是输出电压的上升时间。

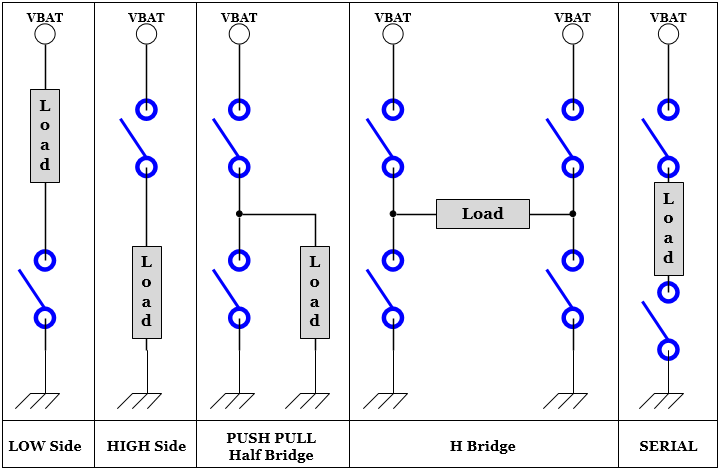

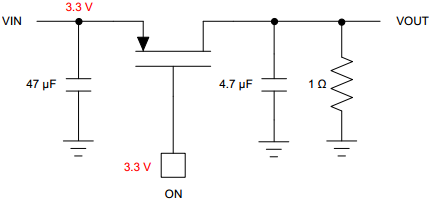

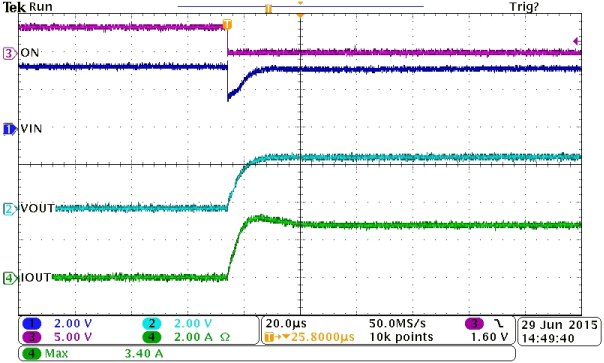

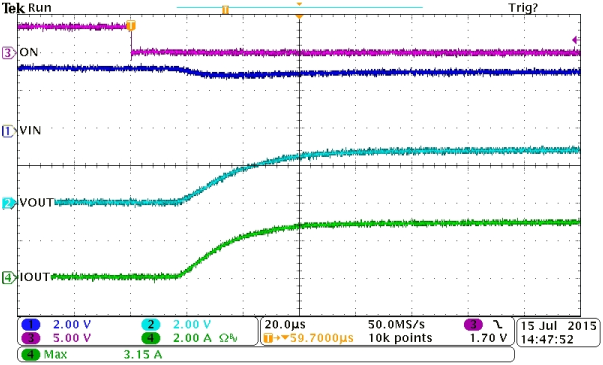

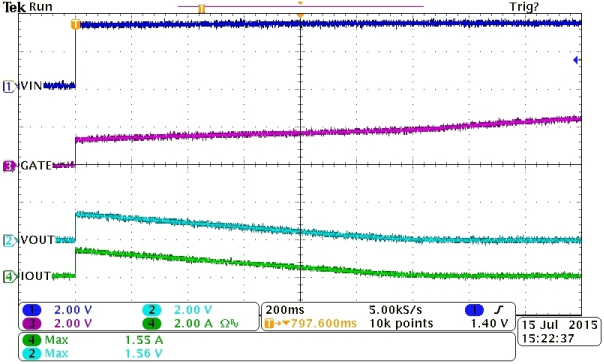

为评估容性负载对浪涌电流的影响,示例图9的 P 型负载开关电路中,负载对地电阻为 1Ω,电容为 4.7µF。选择电路的输入电容是输出电容的 10 倍,以补偿上电瞬间输入电压突降。图10是该电路上电瞬间的波形。当负载开关的控制信号 ON 拉低时,PMOS 导通,负载接入电源 VIN。由于 PMOS 的开启没有控制,负载瞬间的电流需求导致电源输入 VIN 急剧下降,直到电流最终稳定后,VIN 恢复正常值。

图11是将负载电阻移除(删除 1Ω),只包括容性负载(4.7µF)时的上电波形。由此波形可知,在负载电容仅为 4.7µF 时,浪涌电流就有 2A,通过上方浪涌电流的计算公式可知,浪涌电流的大小与负载容性值正相关。

图9. P型晶体管负载开关

图10. PMOS开关的上电波形

图11. PMOS开关的上电波形(仅容性)

开关时间

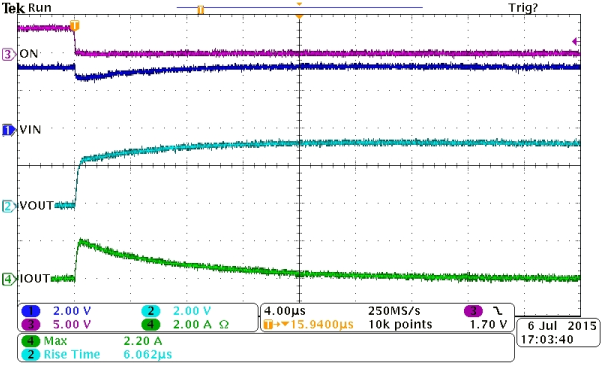

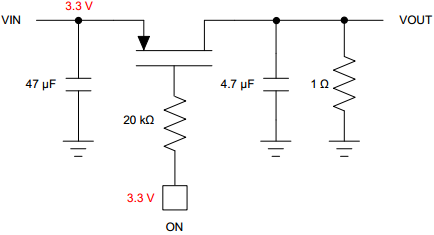

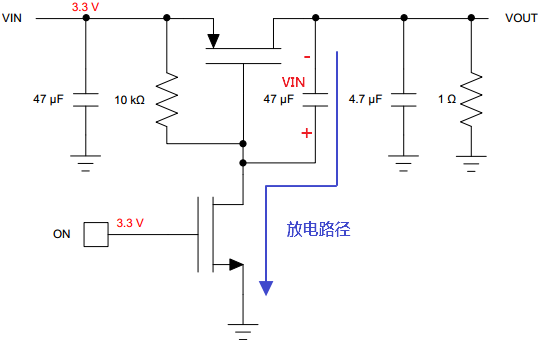

由上文中浪涌电流的计算公式,浪涌电流的大小与输出电压的上升时间成反比。因此可以通过控制晶体管的开关时间,以抑制负载开关浪涌电流。图12表示在 PMOS 的门极串联 20KΩ 电阻控制晶体管开关时间的例子,串接的电阻通过控制MOS管门极充/放电电流的大小,以控制MOS管开关时间。注意,串接的电阻可以延缓负载开关输出电压的上升时间,同时也延长了负载开关的断开时间,设计者需要关注这对有负载快速放电要求应用的影响。图13是门极串接电阻后负载开关闭合瞬间的波形图,从波形可以看到串接的电阻很好地消除了浪涌电流和电源输入电压突降的问题。

图13. PMOS开关的上电波形(在G极串联20K电阻)

然而,对于图14表示的 P 型负载开关电路,存在几个问题:

- 对最高输入电压范围有限制,超出此电压值,无论控制 GPIO 跳变高或低,PMOS 始终导通;

- 通常 Vgs 越高,Rds(on) 越小,而对于上述电路,由于 GPIO 的低电平通常大于等于 0V,也就是说 PMOS 的 Vgs 最高为 Vin,而且如果如果 GPIO 低电平不止 0V,则 Rds(on) 会更高;

- 开关信号为高电平有效,即低电平导通,高电平断开。即负载开关断开时,需要控制器提供为高电平的开关信号,而这意味着控制器不能进入完全休眠或断电状态,并不符合实际应用的要求。

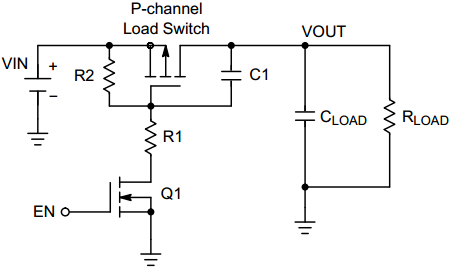

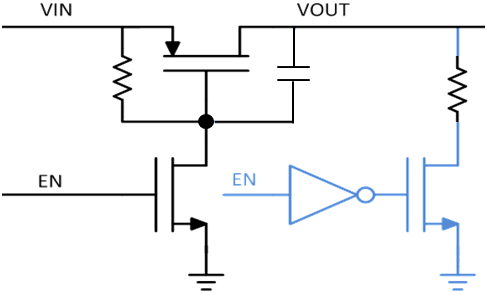

图14表示更常见的 P 型负载开关的控制电路。在此电路的开关控制中使用到 NMOS,这样就不需要 GPIO 一直拉高以断开通流晶体管。另外,该电路允许的最高输入电压(Vin)也与GPIO电压解耦,GPIO电压的差异也不会影响到PMOS门极控制状态。如果输入电压偏小,即 Vgs 偏小,则 Rds(on) 仍然偏大,直接影响到负载开关的效率和压降。电路选择的 C1 的容值要求远大于 Cgd,以保证 C1 对开关时间的影响超过 Cgd。其中 R1 和 R2 电阻分压决定门极电压;R1 和 C1 决定通流晶体管的开关速度,计算公式见链接。

下面通过图15表示的 P 型负载开关缓启控制电路,说明这种类型控制电路的特性和存在的问题。由波形图16示,这种缓启控制电路可以解决上电瞬间的电源突降和浪涌电流问题。然而,负面影响是在上电瞬间 Vout 上有负电压尖刺,这是由于在 ON 信号未使能时,PMOS 的门极悬空,PMOS输出端与门极间电容(47µF)充电至 Vin。当 ON 使能时,PMOS的门极瞬间被拉到地,而电容上的电压不能突变,PMOS的输出端亦被拉低,因此在 Vout 可以检测到负电压的尖刺。当门极的电荷释放完毕后,Vout 正常缓升至 Vin 的电压值。

缓启电容值越小,电压/电流负尖刺的幅值越小,但其控制缓启的效果也越差。设计者须权衡两种效应的影响,负电压尖刺可能会造成设备损坏、闩锁或 ESD 等问题。

图15. P型负载开关缓启电路的放电路径

图16. P型负载开关上电波形(缓启控制)

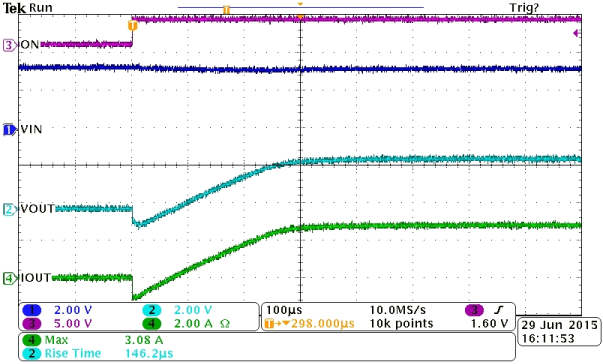

对于图14示意的负载开关缓启控制电路,还存在另外一个问题:在初次施加 Vin 时,由于 PMOS 的门极未充电至Vin,导致 Vgs < 0,这时即使 ON 信号未使能,PMOS还是会打开,电路如图17所示。当缓启控制电容充电至Vin时,PMOS再次关闭。电容充电完毕后,GPIO 才可以正常控制PMOS的开启或关闭,并有缓启控制。但是在初次施加 Vin 时,负载开关会异常开启,且没有缓启控制,电路上电波形如图18所示。这种由 Vin 初次加载引起的负载开关异常开启,以及浪涌电流问题,可能会引起电路设备工作异常,甚至损坏。在例如更换电池时,则可能出现以上情况。

图17. 电源阶跃输入引起的异常开启问题

图18. P型负载开关Vin的阶跃特性

附加特性

本章主要介绍负载开关电路的附加功能特性和保护特性。附加功能特性包括快速放电和电源正常指示,保护特性包括电压电流反向保护、限流保护、欠压锁定、过流过压过温保护等。

快速放电

快速放电(QOD, Quick Output Discharge)功能是指在负载开关断开时,将负载开关的输出端(通过电阻)接地。快速放电可以防止负载开关输出端悬空,保持在确定的状态,并保证下游设备完全掉电。图19蓝色部分表示由分立元件构造的快速放电电路,快速放电电路包一个反相器和一个放电控制晶体管。

注意,并非所有应用都需要负载开关包括快速放电功能,比如使用负载开关实现的多路电源选择电路,如果任何负载开关有QOD功能,则会形成电源到地的路径,影响其它负载开关正常工作。另外,对于包括电池的应用,快速放电电路会耗尽电池的能量。

图19. 快速放电电路

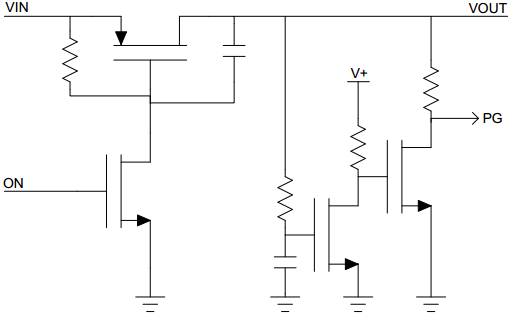

电源正常指示

电源正常指示(PG, Power Good),即表示负载开关输出正常的信号。PG典型的实现电路如图20所示,该电路需要另外一路电源 V+,让PG在Vout没有输出时输出为低。如果PG的电平与Vout不一致,则该电路还需要另外一路电源,将PG上拉到该电源的电平。

PG可以用来通知下游设备电源正常,进行时序控制或者作为上电的反馈信号提供给控制器。

图20. Power Good 电路

反向保护

反向电流保护(RCB, Reverse Current Blocking),防止负载开关断开时电流由 Vin 流向 Vout,其典型电路如图21示,是由两个背靠背的场效应晶体管实现的。

图21. 反向电流保护

限流保护

限流保护是指防止负载开关上提供的电流值超过电源输出能力。过流可能损坏电源、系统或负载设备。图22示意由电流采样电阻和运放比较器实现的限流保护电路,比较器的输出控制负载开关的通断。由于比较器关闭负载开关存在时延,当输出端电流过大,反过来又将负载开关打开,因此形成输出电压振荡。通过在比较器输出端增加 RC,可以削弱振荡的程度,但并不能完全消除之。同时,RC 电路也延缓了负载开关闭合和断开的时间。

图22. 限流保护电路

欠压锁定

欠压锁定(UVLO, Undervoltage lock-out ),在电源电压降低到一定程度时,切断电源输出以防止对设备造成损坏。图23表示由分立元件实现的欠压锁定电路,由电源输入端分压,接入到运放比较器,用比较器的输出控制负载开关的门极。当输入电压的分压低于比较器的参考电压时,比较器输出控制负载开关断开,从而将负载从电源上断开。

图23. 欠压闭锁电路

过热保护

过热保护(TSD, Thermal shutdown),通常由温度传感器芯片或热敏电阻测量负载开关温度,在温度超过一定限值时断开输出。集成式的负载开关芯片一般会包括过热保护功能。

总结

虽然可以通过分立电路设计规避负载开关方案的某些缺陷,但电路仍相对复杂。集成负载开关芯片相比于分立式方案,在电路设计上更加简单,而且布局更加紧凑,从而节省单板空间。集成式负载开关不但可以提供丰富的电路保护功能,还可以通过实现简单而有效的电源分配网络,降低系统的总功耗。

市场上主流的半导体供应商,如 TI, ON, NXP, Infineon, ST 等都有集成式负载开关产品可供选择。

参考资料

1. Smart High Side Switches: What the designer should know? -Infineon

2. AND9093/D: Using MOSFETs in Load Switch Applications -ON

3. SLVA652: Basics of Load Switches -TI

4. SLVA716: Integrated Load Switches versus Discrete MOSFETs -TI

5. SLVA887: Selecting a Load Switch to Replace a Discrete Solution -TI

6. What is a high-side/low-side driver in electronics? -Quora

牛逼!